# Hardware SPICE

| Version Control |                           |

|-----------------|---------------------------|

| Version:        | 2.0                       |

| Release date:   | Dec 18 <sup>th</sup> 2020 |

| Distribution    | Public                    |

| Status          | Released                  |

### Content

| 1      | Documen     | t Scope                                                                   | 4  |

|--------|-------------|---------------------------------------------------------------------------|----|

|        | 1.1         | Contributors                                                              | 4  |

|        | 1.2         | Trademarks                                                                | 4  |

|        | 1.3         | Copyright Notice                                                          | 4  |

|        | 1.4         | Document History                                                          | 5  |

|        | 1.5         | Distribution of This Document                                             | 5  |

|        | 1.6         | Change Request Handling                                                   | 5  |

|        | 1.7         | References                                                                | 5  |

|        | 1.8         | Terms, Definitions, and Abbreviations                                     | 7  |

| 2      | Introductio | on                                                                        | 11 |

|        | 2.1         | Purpose                                                                   | 11 |

|        | 2.2         | Scope                                                                     | 11 |

|        | 2.3         | Community of Interest                                                     | 12 |

|        | 2.4         | Automotive SPICE® plug-in candidate vs. standalone use                    | 12 |

| 3      | Key Conc    | epts                                                                      | 13 |

|        | 3.1         | Recollection – Understanding of a PRM                                     | 13 |

|        | 3.2         | Rationales, General                                                       | 15 |

|        | 3.3         | Rationales for HWE.1                                                      | 16 |

|        | 3.4         | Rationales for HWE.2                                                      | 19 |

|        | 3.5         | Rationales for HWE.3 and HWE.4                                            | 21 |

|        | 3.6         | Addressing the Mixture of Requirements and Design                         | 23 |

|        | 3.7         | Notion of 'System' above HWE Processes                                    | 24 |

|        | 3.8         | Agile Approaches                                                          | 24 |

|        | 3.9         | ISO 26262 Mapping                                                         | 25 |

|        | 3.10        | Automotive SPICE® PAM                                                     | 26 |

|        | 3.11        | VDA BlueGoldBook 'Automotive SPICE® Guidelines' [20]                      | 28 |

| 4<br>R |             | Reference Model, Performance Indicators (CL1), Rating Rules, Rating tions | 29 |

|        | 4.1         | HWE.1 – Hardware Requirements Analysis                                    | 29 |

|        | 4.2         | HWE.2 – Hardware Design                                                   | 34 |

|        | 4.3         | HWE.3 – Verification against Hardware Design                              | 39 |

|        | 4.4         | HWE.4 – Verification against Hardware Requirements                        | 43 |

| 5      | Process C   | Capability Levels and Process Attributes                                  | 46 |

| A      | nnex A 🛛 Wo | ork Product Characteristics (WPC)                                         | 47 |

| Annex A.1 | 1 [  | Motivation                                     |

|-----------|------|------------------------------------------------|

| Annex A.2 | 2 ۱  | WPC in this Document                           |

| Annex B   | Con  | formity of the HWE PRM/PAM50                   |

| Annex B.1 | 1 I  | Introduction                                   |

| Annex B.2 | 2 (  | Conformance to the requirements for PRMs50     |

| Annex B.3 | 3 (  | Conformance to the requirements for PAMs50     |

| Annex C   | Prop | posals for Automotive SPICE <sup>®</sup>       |

| Annex C.1 | 1 [  | MAN.3 Project Management                       |

| Annex C.2 | 2 5  | SYS.2 System Requirements Analysis             |

| Annex C.3 | 3 5  | SYS.3 System Architectural Design              |

| Annex C.4 | 4 9  | SYS.4 System Integration Testing               |

| Annex C.5 | 5 5  | SYS.5 System Qualification Testing             |

| Annex C.6 | 6 9  | SWE.2 Software Architectural Design57          |

| Annex C.7 | 7 5  | SPL.2 Product Release                          |

| Annex C.8 | 8 ۱  | WPC 13-21 Change Control Record 58             |

| Annex C.9 | 9 ۱  | ۷PC 13-22 Traceability Record 5٤               |

| Annex C.1 | 10 ۱ | WPC 17-08 Interface requirements specification |

| Annex C.1 | 11 F | Further proposals                              |

| Annex D   | Con  | tact Persons                                   |

| Annex E   | Chai | nge History61                                  |

# 1 Document Scope

# 1.1 Contributors

The following companies have contributed to the creation of this document (alphabetical order):

ART S.p.A., Audi AG, Brose Fahrzeugteile SE & Co. KG, Continental Automotive GmbH, Car.Software-Organisation (subsidiary within the Volkswagen Group), DräxImaier Group, Exida Group, Infineon, ITK Engineering GmbH, Kugler Maag Cie GmbH, Lorit Consultancy GmbH, Preh GmbH, Robert Bosch GmbH, Schaeffler Technologies AG & Co. KG, Sharpen360, SynSpace Group GmbH, Valeo Siemens eAutomotive Germany GmbH, WABCO GmbH & Co. KG, ZF Friedrichshafen AG

Direct contact partners of the respective companies see Annex D.

# **1.2 Trademarks**

Automotive SPICE<sup>®</sup> is a registered trademark of the 'Verband der Automobilindustrie e.V.' (VDA). For further information about Automotive SPICE<sup>®</sup> visit <u>www.automotivespice.com</u>.

intacs<sup>™</sup> is a registered trademark.

# **1.3 Copyright Notice**

Copyright 2018-2019 International Assessor Certification Scheme e.V. (hereafter referred to as intacs). All rights reserved.

Redistribution and use with or without modification are permitted provided that redistribution reproduces the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials provided with the distribution.

THIS DOCUMENTATION IS PROVIDED BY INTACS 'AS IS' AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL INTACS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS DOCUMENTATION, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE

This document may reproduce relevant material from:

■ ISO/IEC 33020:2015 (Information technology -- Process assessment -- Process measurement framework for assessment of process capability).

It provides the following copyright release statement:

'Users of this International Standard may reproduce clauses 5.2, 5.3, 5.4 and 5.6 as part of any process assessment model or maturity model so that it can be used for its intended purpose.'

Relevant material from one of the mentioned standards is incorporated under the copyright release notice.

■ The Automotive SPICE® Process Reference Model and Process Assessment Model Version 3.x for which permission has been granted by the SPICE User Group and the VDA QMC.

Automotive SPICE® is a registered trademark of the 'Verband der Automobilindustrie e.V.' (VDA).For further information about Automotive SPICE® visit <u>www.automotivespice.com</u>.

# **1.4 Document History**

| Version | Date        | Ву                                                       | Notes                                                                                                                                                                           |

|---------|-------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0     | Nov 15 2019 | Pierre Metz<br>intacs™ Advisory Board member             | 1 <sup>st</sup> release                                                                                                                                                         |

| 2.0     | Dec 18 2020 | Pierre Metz<br>intacs <sup>™</sup> Advisory Board member | <sup>2nd</sup> release. Details see "Annex E - Change<br>History". Independent ISO/IEC 33020<br>compliance review, and confirmation, by<br>Mr. Petr Švimberský, Czech Republic. |

# **1.5** Distribution of This Document

Released versions of this document can be obtained freely from the <u>www.intacs.info</u> website. It is permitted for the recipient to further distribute this document without modification.

# 1.6 Change Request Handling

Any problems or change requests shall be reported via the ticketing system on <u>www.intacs.info</u>. Please add the prefix 'HWE PRM/PAM' to the subject of your ticket.

In order for a change request to be processed it must contain

- 1. a detailed problem description

- 2. an elaborated argumentation why a particular rationale is false or incomplete

- 3. a change proposal

# 1.7 References

- [1] ISO/IEC 33001:2015, Information technology -- Process assessment Concepts and terminology

- [2] ISO/IEC 33002:2015 Information technology -- Process assessment Requirements for performing process assessment

- [3] ISO/IEC 33003:2015 Information technology -- Process assessment Requirements for process measurement frameworks

- [4] ISO/IEC 33004:2015 Information technology -- Process assessment Requirements for process reference, process assessment and maturity models

- [5] ISO/IEC 33020:2015 Information technology -- Process assessment Process measurement framework for assessment of process capability

- [6] ISO/IEC/IEEE 29119-1:2013 Software and systems engineering -- Software testing -- Part 1: Concepts and definitions

- [7] ISO/IEC/IEEE 29119-3:2013 Software and systems engineering -- Software testing -- Part 3: Test documentation

- [8] ISO/IEC/IEEE 24765:2017 Systems and software engineering -- Vocabulary

- [9] ISO/IEC 25010:2011 Systems and software engineering Systems and software Quality Requirements and Evaluation

- [10] ISO 26262-1:2018 "2<sup>nd</sup> Edition"

- [11] ISO 26262-2:2018 "2nd Edition"

- [12] ISO 26262-4:2018 "2nd Edition"

- [13] ISO 26262-5:2018 "2nd Edition"

- [14] ISO 26262-6:2018 "2nd Edition"

- [15] ISO 26262-8:2018 "2nd Edition"

- [16] ISO 26262-9:2018 "2<sup>nd</sup> Edition"

- [17] ISO 26262-10 "2<sup>nd</sup> Edition"

- [18] ISO 26262-11:2018 "2nd Edition"

- [19] Automotive SPICE® Process Reference Model/Process Assessment Model, v3.1, VDA QMC

- [20] VDA BlueGoldBook 'Automotive SPICE® Guidelines', 1st. edition, September 2017, VDA, Quality Management in the Automotive Industry

- [21] P.Metz, 'Capability Level 2 und 3 in der Praxis', dpunkt Verlag, 2016

- [22] SoQrates Process Assessment Model: SPICE for Hardware Engineering, version 1.0, 30.01.2018, http://soqrates.eurospi.net/images/meetings/files/hwe\_spice\_1.00.pdf

- [23] Process Assessment Model Automotive SPICE for Mechanical Engineering, public release, v1.5 as of Dec 6<sup>th</sup> 2018, intacs working group Mechanical SPICEs

- [24] IATF 16949:2016-10 Quality management system requirements for automotive production and relevant service parts organisations

- [25] ISO IEC IEEE 29148, Systems and software engineering Life cycle processes Requirements engineering

- [26] IREB, Requirements Engineering Fundamentals: A Study Guide for the Certified Professional for Requirements Engineering Exam - Foundation Level - IREB (CPRE) compliant, <u>https://www.ireb.org/de</u>

- [27] ISO IEC IEEE 24765, Systems and software engineering Vocabulary

- [28] INCOSE Guide for Writing Requirements (TP-2010-006-01)

- [29] intacs™ certified Provisional Assessor standard training course materials, 2020

- [30] intacs<sup>™</sup> white paper 'Clarifying Myths with Process Maturity Models vs. Agile', v1.0 of Aug 6<sup>th</sup> 2014, F.Besemer/T.Karasch/P.Metz/J.Pfeffer, see <u>www.intacs.info</u>

# **1.8 Terms, Definitions, and Abbreviations**

| shall  | means that compliance with a statement is mandatory for compliance with an assessment indicator                        |

|--------|------------------------------------------------------------------------------------------------------------------------|

| should | means that compliance with a statement is recommended but is not mandatory for compliance with an assessment indicator |

| may    | is used to describe a permissible way to achieve compliance with an assessment indicator                               |

References to ISO 26262:2018 have been added throughout the HWE PRM/PAM in blue colour text, see clause 3.9.1.

| Term             | Reference                                              | Description                                                                                                                                                                                                                                                                   |

|------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AOI              | intacs <sup>™</sup> working<br>group 'HW<br>processes' | Automated Optical Inspection                                                                                                                                                                                                                                                  |

| AXI              | intacs <sup>™</sup> working<br>group 'HW<br>processes' | Automated X-Ray Inspection                                                                                                                                                                                                                                                    |

| ASIL             | ISO 26262                                              | Automotive Safety Integrity Level                                                                                                                                                                                                                                             |

| BGB              | VDA                                                    | Automotive SPICE® Guidelines ('BlueGoldBook')                                                                                                                                                                                                                                 |

| BP               | ISO/IEC 330xx                                          | Base Practice                                                                                                                                                                                                                                                                 |

| Characterisation | intacs <sup>™</sup> working<br>group 'HW<br>processes' | In semiconductor development a post-silicon process of determining the fundamental electrical and physical characteristics of a device based on statistical analysis (cf. ISO26262-5:2018, clause 10.4, Table 11). Equals e.g. electrical and functional testing of hardware. |

| CL               | ISO/IEC 330xx                                          | Capability Level                                                                                                                                                                                                                                                              |

| CR               | intacs <sup>™</sup> working<br>group 'HW<br>processes' | Change Request                                                                                                                                                                                                                                                                |

| DFA              | [10], [16] clause 7<br>and Annex C                     | Dependent Failure Analysis                                                                                                                                                                                                                                                    |

| ECU              | Automotive SPICE®<br>PRM/PAM                           | Electronic Control Unit                                                                                                                                                                                                                                                       |

| EOL              | intacs <sup>™</sup> working<br>group 'HW<br>processes' | End-of-Line                                                                                                                                                                                                                                                                   |

| ΕΤΑ              | intacs <sup>™</sup> working<br>group 'HW<br>processes' | Event Tree Analysis                                                                                                                                                                                                                                                           |

| FMEA             | intacs <sup>™</sup> working<br>group 'HW<br>processes' | Failure Mode and Effect Analysis                                                                                                                                                                                                                                              |

#### Table 1 – Terminology

| FMECA                        | intacs <sup>™</sup> working<br>group 'HW               | Failure Mode and Effects and Criticality Analysis                                                                                                                             |

|------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FMEDA                        | processes'<br>intacs <sup>™</sup> working              | Failure Modes, Effects and Diagnostic coverage Analysis                                                                                                                       |

|                              | group 'HW<br>processes'                                |                                                                                                                                                                               |

| FTA                          | intacs <sup>™</sup> working<br>group 'HW<br>processes' | Fault Tree Analysis                                                                                                                                                           |

| GDSII                        | intacs <sup>™</sup> working<br>group 'HW<br>processes' | Graphical Design Station II or Graphic Data System II                                                                                                                         |

| GP                           | ISO/IEC 330xx                                          | Generic Practice                                                                                                                                                              |

| Hard-macro                   | ISO 26262                                              | A physical representation of an IP (ISO 26262-11:2018, clause 5.1.5 Table 30)                                                                                                 |

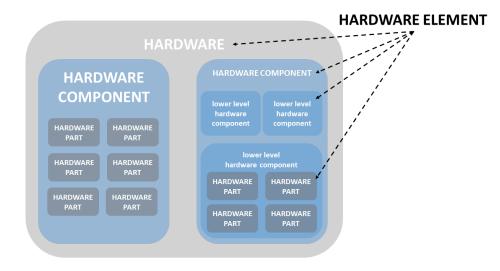

| Hardware                     | intacs <sup>™</sup> working<br>group 'HW<br>processes' | Assembled and interconnected physical hardware components or parts which perform analog or digital functions or operations.<br>See Figure 1.                                  |

|                              |                                                        | NOTE: this can refer to a fully assembled PCB, or a microcontroller at the semiconductor level.                                                                               |

|                              |                                                        | NOTE: conceptually, the term 'hardware' can be compared to binary after SW build in the software domain.                                                                      |

| Hardware<br>component        | intacs <sup>™</sup> working<br>group 'HW<br>processes' | Logical (e.g. functional block) or physical group of hardware parts realising a functionality, which                                                                          |

|                              |                                                        | <ul> <li>cannot be realised by any of its hardware parts alone, e.g.<br/>voltage monitoring, power supply.</li> </ul>                                                         |

|                              |                                                        | <ul> <li>may be organised hierarchically, i.e. a hardware component can<br/>contain lower-level hardware components.</li> </ul>                                               |

|                              |                                                        | See Figure 1.                                                                                                                                                                 |

|                              |                                                        | NOTE: Depending on the application, e.g. the populated PCB, a system-<br>on-chip, a microcontroller, or an SBC can be considered a HW component.<br>See also clause 3.7 here. |

| Hardware<br>development only | intacs <sup>™</sup> working<br>group 'HW<br>processes' | Hardware development only refers to projects where hardware is developed without system, software, and mechanical development.                                                |

| Hardware<br>element          | intacs <sup>™</sup> working<br>group 'HW<br>processes' | Generic term, can represent a hardware component, a hardware part, or the hardware. See Figure 1.                                                                             |

| Hardware item                | intacs™ working<br>group 'HW<br>processes'             | Regarding the term 'item', Annex D.3 in [19] applies correspondingly.                                                                                                         |

| Hardware part                | intacs <sup>™</sup> working<br>group 'HW               | Fundamental HW element the purpose and functionality of which cannot be further subdivided or separated.                                                                      |

|                              | processes'                                             | See Figure 1.                                                                                                                                                                 |

|                              |                                                        | NOTE: Examples are transistors, resistors, diodes, non-populated PCB                                                                                                          |

|                              |                                                        | NOTE: Depending on the application, e.g. a system-on-chip, a microcontroller or an SBC can be considered a HW part. See clause 3.7 here.                                      |

|                                    |                                                        | NOTE: the term 'unit' is considered to apply to the software domain only.<br>The term 'hardware part' can be viewed as the hardware counterpart of<br>'software unit'.                                                                                                 |

|------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HW                                 | intacs <sup>™</sup> working<br>group 'HW<br>processes' | Abbreviation for electrical or electronic 'hardware'                                                                                                                                                                                                                   |

| HWE                                | Automotive SPICE®<br>PRM/PAM                           | 15504/330x-compliant lifecycle processes for hardware engineering                                                                                                                                                                                                      |

| ICT                                |                                                        | In-circuit-test                                                                                                                                                                                                                                                        |

| INCOSE                             | https://<br>www.incose.org                             | International Council on Systems Engineering                                                                                                                                                                                                                           |

| IP                                 | intacs <sup>™</sup> working<br>group 'HW<br>processes' | Intellectual Property<br>A reusable unit of logical or physical design to be integrated into a design<br>as a part of a component (ISO 26262-11:2018, clause 4.5).<br>See also term 'hard-macro' and 'soft-macro'.                                                     |

| PA                                 | ISO/IEC 330xx                                          | Process Attribute                                                                                                                                                                                                                                                      |

| PAM                                | ISO/IEC 330xx                                          | Process Assessment Model                                                                                                                                                                                                                                               |

| Pre-Silicon<br>Verification        | intacs <sup>™</sup> working<br>group 'HW<br>processes' | Semiconductor design verification, generally performed as simulation or review without physical hardware. See also term 'Post-Silicon Verification'. (ISO 26262-11:2018, clause 4.8.1; clause 4.12 Table 27, Table 28; clause 5.1.9 Table 31; clause 5.3.5.3 Table 52) |

| Post-Silicon<br>Verification       | intacs <sup>™</sup> working<br>group 'HW<br>processes' | Verification of produced semiconductor (i.e. "on target"). It corresponds to "classical" testing of hardware. (ISO 26262-11:2018, clause 4.12 Table 27, Table 28)                                                                                                      |

|                                    |                                                        | See also terms 'Pre-Silicon Verification' and 'Tape-Out'.                                                                                                                                                                                                              |

| PRM                                | ISO/IEC 330xx                                          | Process Reference Model                                                                                                                                                                                                                                                |

| Qualification of<br>hardware parts | intacs <sup>™</sup> working<br>group 'HW<br>processes' | Verification proceeding to assure lifetime reliability of hardware parts<br>under specified environmental conditions mostly performed according to<br>well-defined industry standards such as AEC-Q100 and JEDEC.                                                      |

| RC                                 | BGB [20]                                               | Rating Recommendation                                                                                                                                                                                                                                                  |

| RL                                 | BGB [20]                                               | Rating Rule                                                                                                                                                                                                                                                            |

| RTL                                | intacs <sup>™</sup> working<br>group 'HW<br>processes' | Register Transfer Level                                                                                                                                                                                                                                                |

| Special<br>characteristics         | See Annex A, 11-HW                                     | 02                                                                                                                                                                                                                                                                     |

| SPICE                              | Adapted from<br>ISO/IEC 15504,<br>ISO/IEC 330xx        | Systems/Software Process Improvement and Capability Determination                                                                                                                                                                                                      |

| Soft-macro                         | ISO 26262                                              | A model representation of an IP in terms of hardware description language (HDL) or analogue transistor level circuit schematic                                                                                                                                         |

| Tape-Out                           | intacs <sup>™</sup> working<br>group 'HW<br>processes' | Final step of the semiconductor design process for integrated circuits at which the graphic for the photomask of the circuit (GDSII) is sent to the fabrication facility.                                                                                              |

|                                    |                                                        | It denotes the transition from the pre- to the post-silicon development phase.                                                                                                                                                                                         |

| Verification<br>measure      | intacs <sup>™</sup> working<br>group 'HW<br>processes' | Verification measure is a generic umbrella term for test cases, measurements, calculations, simulations, reviews, and analyses. |

|------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Verification<br>measure data | intacs <sup>™</sup> working<br>group 'HW<br>processes' | Verification measure data are data recorded during the execution of a verification measure.                                     |

| WCCA                         |                                                        | Worst Case Circuit Analyses                                                                                                     |

| WG                           | intacs <sup>™</sup> working<br>group 'HW<br>processes' | Working Group                                                                                                                   |

| WP                           | ISO/IEC 330xx                                          | Work Product Indicator                                                                                                          |

| WPC                          | ISO/IEC 330xx                                          | Characteristics for Work Product Indicators                                                                                     |

Figure 1 – Graphical representation of hardware, hardware component, hardware part, hardware element

# 2 Introduction

This document contains the Hardware Engineering Process Reference Model (PRM) and Process Assessment Model (PAM), hereinafter called 'HWE PRM/PAM', as integral parts.

# 2.1 Purpose

The purpose of this document is to define a PRM and a PAM for Hardware Engineering, in order to assure that assessments are resulting into a set of process profiles in a repeatable and reliable manner, according to ISO/IEC 33004 [4].

# 2.2 Scope

In [20], section 'Introduction' the VDA informs that

'The objective of working group 13 is the definition of the Automotive SPICE process reference and assessment model. In addition to that, it is the objective of the working group to give necessary clarifications and recommendations for the application of Automotive SPICE ...

To fulfill this mandate, the following activities were performed:

Improving the Automotive SPICE Process Assessment and Reference Model regarding structure, inconsistencies, clarifications and additional concepts. This was done with the publication of the 3.0 version of Automotive SPICE in July 2015

... Giving guidelines on the interpretation of Automotive SPICE and on Assessment performance. This is provided by [the VDA BlueGoldBook 'Automotive SPICE® Guidelines] in 2017.'

This means that a full understanding about Automotive SPICE<sup>®</sup> is provided in two distinct documents, i.e. the Automotive SPICE<sup>®</sup> PRM/PAM and the BlueGoldBook (BGB). Further, even though the BGB is called 'Guidelines' that are recommended by the VDA to be followed by its members, its content can be considered 'normative expectations'. This can be concluded from the fact that e.g. a deviation of a full rating rule (RL) requires a documented justification in the assessment report by the assessor responsible.

In order to

- reduce the number of documents needed

- provide assessment indicators that are as expressive and rich as the BGB

this HWE PRM/PAM integrates the 'HWE PRM/PAM guidelines' (i.e. there is no separate 'HWE PRM/PAM guideline' document). This is done by directly strengthening base practices, adding informative notes, and providing rating rules and recommendations on top of the PAM directly below the corresponding process.

### 2.2.1 Technical Scope

The technical scope of this document is electrical or electronic hardware engineering. This excludes:

- system level engineering, i.e. neither the mechatronic nor the ECU level (see clause 3.7). See also the definition of the term "hardware" in clause 1.8;

- procurement (see clause 3.2);

- mechanical or hardware sample manufacturing (see clause 3.2);

- production processes (see clause 3.2).

However, process interfaces are included to

- procurement in terms of receiving physical design-compliant hardware parts;

- production and prototype/sample workshops in terms of providing information such as production data and requirements, and receiving compliant samples, respectively.

# 2.3 Community of Interest

This HWE PRM/PAM has been created

- taking into consideration the work provided by the SoQrates initative [22];

- by consensus of supplier and consultancy companies based in several European countries organised in a working group set up and monitored by intacs<sup>TM</sup> (www.intacs.info); during the creation of this document since Feb 2018 this working group has received an increasing number of inquiries about its status and content. This proves that there is a community of interest in the automotive industry;

- in accordance with the requirements of ISO/IEC 33004 [4] (see Annex B).

# 2.4 Automotive SPICE® plug-in candidate vs. standalone use

Further, this document

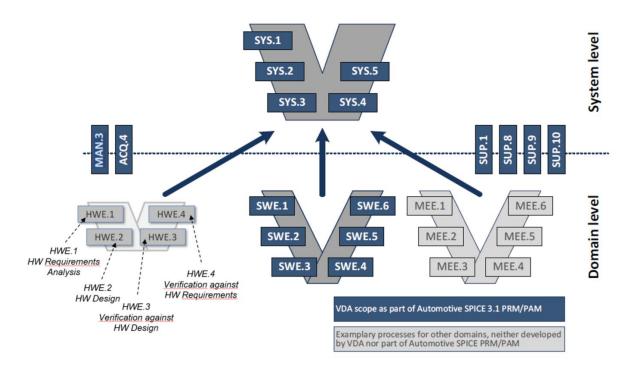

can serve as a proposal for a hardware domain plug-in for the Automotive SPICE® [19] Plug-In concept introduced in Automotive SPICE<sup>®</sup> version 3.0. In order to meet copyrights, and not to create redundancy, full process definitions and related indicators in Automotive SPICE<sup>®</sup> have not been included into this document. Instead, references to the currently valid Automotive SPICE<sup>®</sup> version 3.1 are used. Also note that in order for Automotive SPICE<sup>®</sup> to also represent an actual mechatronic or ECU system level, necessary changes to Automotive SPICE<sup>®</sup> are advised in Annex C.

Figure 2 – Sketch of the plug-in concept, based on the corresponding Figure in [19]

■ can be used standalone for the assessment of process capability of hardware development only. In such a case, any reference to Automotive SPICE® PRM/PAM elements, or any other system level aspects above the HWE PRM/PAM, do not apply.

# 3 Key Concepts

# 3.1 Recollection – Understanding of a PRM

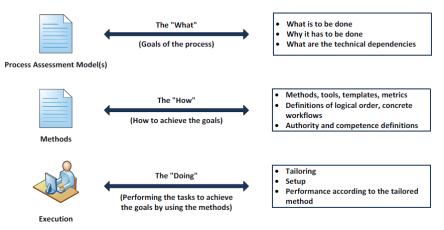

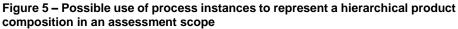

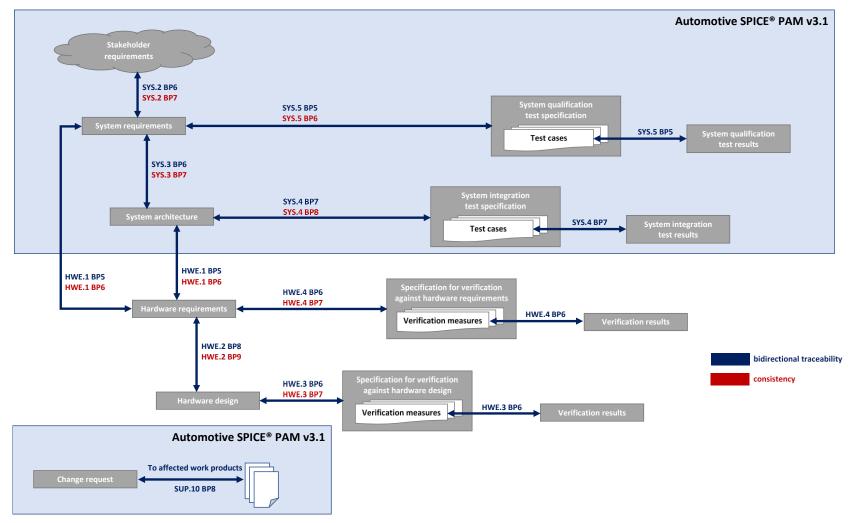

A PRM/PAM are at the level of the WHAT by abstracting from any HOW level, see Figure 3:

Figure 3 – Levels of abstraction of a PRM/PAM according to [19] clause 3.3.3

A 'process' in a PRM according to [4] groups a set of coherent and related characteristics of a particular technical topic at the WHAT level ('distinct conceptual silo'). As a consequence:

A PRM/PAM does not represent or demand a particular lifecycle model. Generally, a process lifecycle model, among other elements, defines a logical order of phases, activities, workflows, and parallelisation. Lifecycle models therefore are a concept of a HOW level. For example, this is made visible in Automotive SPICE<sup>®</sup> MAN.3 Project Management BP2 "Define project life cycle".

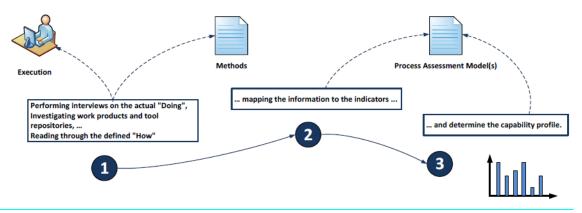

A HOW level will detail out a lifecycle model by denoting a company's or HW department's proceedings such as describing the organisational interactions and interfaces, roles, tool chains, and documents. In this respect, it is the assessor's responsibility to perform a mapping of elements in such a HOW level to the Assessment Indicators in the PAM (see [19] clause 3.3.3), see Figure 4.

Figure 4 – mapping of Assessment Indicators, according to [19] clause 3.3.3

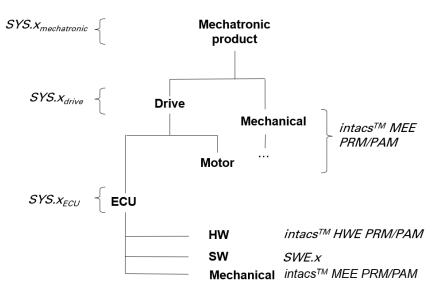

The processes in a PRM or PAM do not represent product hierarchies, i.e. neither are the Automotive SPICE SYS.x processes supposed to solely represent a particular level only (e.g. mechatronic system, drive, or ECU), nor does the HWE PRM/PAM represent an ECU level (see clause 2). In order to explicitly address the process capability of distinct product hierarchy levels, corresponding process instances would have to be defined in the assessment scope (see [20] clause 1.2), as illustrated in Figure 5.

# 3.2 Rationales, General

### 3.2.1 Rationale 1 – No Production Process

This document defines a Process Reference Model (PRM) and Process Assessment Model (PAM) for Hardware Engineering and is therefore not intended to define an assessment model for production processes.

To avoid redundancies and potential inconsistencies with other international standards having production in scope such as IATF 16949, PRM and PAM counterparts of production processes are not included at all.

Correspondingly, there is no process for prototype and sample construction/workshops (German: 'Musterbau') either.

For these reasons, 'process interfaces' to the production domain are required. In this HWE PRM/PAM this is achieved by means of

- output work product characteristics for HWE.2:

- 11-HW01 Hardware Production Data

- 11-HW02 Special Characteristics

- 04-HW04 Bill of Materials

- the BP 'Ensure use of compliant samples', including comprehensive Notes, for HWE.3 and HWE.4

### 3.2.2 Rationale 2 – No Procurement Process

Further, no hardware element procurement process is introduced in this HWE PRM/PAM for the following reasons:

- HW development is requirements-driven. Therefore, what matters is compliance to the requirements for the respective environment, irrespective of the source from which HW parts are obtained. Verification (HWE.3, HWE.4) will demonstrate that the physical product or sample is compliant with the HW design and with HW requirements.

- There is no predefined standard for procurement at the level of abstraction of a PRM/PAM beyond what is IATF 16949. Thus, defining a procurement process here would have required the cooperation with other parties competent in the procurement domain. The identification of, and collaboration with, such would have significantly delayed the HW PAM publication date.

A 'process interface' to procurement can be considered existent by means of

■ BP 'Develop hardware detailed design' in HWE.2, together with Note 8.

# 3.3 Rationales for HWE.1

### 3.3.1 Rationale 3 – Requirements Characteristics at CL1

The state-of-the-art in requirements engineering (reflected in standards such as ISO IEEE 29148 [25] or ISO 26262-8:2018) requires each single requirement to reveal particular characteristics in order to actually represent a requirement (see also clause 3.6 here). Only one of these is 'verifiability'.

For this reason, HWE.1.BP1 is appended with '...according to state-of-the-art characteristics for requirements' together with Note 2. This is because a requirements specification not following the state-of-the-art

- introduces significant process risk in terms of giving rise to systematic faults, especially in downstream design, realisation, and verification activities, and

- thus, can hardly represent a full achievement of a requirements process purpose at CL1.

Correspondingly, in HWE.1.BP3 there is no term 'verifiability'; the reason is requirements that are non-compliant with such characteristics would probably lead to a downrating of both BP1 and BP3. This would represent double punishment which would not be consistent with the philosophy of a process assessment model.

Note that this strengthening of HWE.1.BP1 is not in conflict, or an overlapping, with GP 2.2.1 of CL2. Reasons:

- GP 2.2.1 addresses more than quality criteria such as structural requirements (e.g. by means of templates), checklists etc.

- In [21] it has already been suggested, and explained, for the

- requirements-oriented processes SYS.2 and SWE.1

- design-oriented processes SWE.2 and SWE.3

which quality criteria exactly are to be tied to the process purpose at CL1, and which quality criteria are relevant in the context of GP 2.2.1 at CL2, and why.

### 3.3.2 Rationale 4 – No Extra Verification Criteria Base Practice

The Automotive SPICE® v3.1 PAM explains the 'verification criteria' concept as follows:

'BP5. Develop the verification criteria for each software requirement that define the qualitative and quantitative measures for the verification of a requirement. [OUTCOME 2, 7]

NOTE 6: Verification criteria demonstrate that a requirement can be verified within agreed constraints and is typically used as the input for the development of the software test cases or other verification measures that should demonstrate compliance with the software requirements.

The BGB [20] elaborates on this in clause 2.1.3 by explaining:

Verification criteria are not the same as test cases, but are input to them. Verification criteria are necessary ... to understand the preconditions for the test of a single requirement or a set of requirements. The requirements engineer should share this knowledge with the tester through the verification criteria.'

Based on this, in practice there have been two views on what verification criteria can represent:

View 1. The characteristic of 'verifiability' of each requirement.

View 2. There may be 'explicit additional verification criteria' on top of what a requirement already says, and that are passed on, such as '*Identification of a verification method or verification step (e.g. software test, system test) is necessary, ... special test methods, environments, ...*' [BGB [20], clause 2.1.3.1].

Recall that view (1.) is covered by HWE.1.BP1 (see 'Rationale 3 – Requirements Characteristics at CL1').

A critical observation in practice regards to view (2.) however is:

- It is optional. It cannot be considered a *mandatory* part of a requirements process purpose to provide suggestions on verification or testing. Therefore, this should not be a part of a base practice because according to ISO/IEC 33004 in a PAM a base practice is a normative indicator<sup>1</sup>.

- Preconditions', 'verification methods', 'verification environment' are testing concerns, and therefore are a part of a test specification or verification strategy. These are not requirements concerns. This observation is further supported by the following facts: the BGB rules for verification criteria technically overlap

- with those for SWE.6.BP1

- with those for SYS.5.BP1 (see [20] clauses 3.11.1.1 and 3.5.1.1)

This would mean that, firstly, in absence of any verification environment and methods, BP1 of both SWE.1 and SWE.6 (or SYS.2 and SYS.5 respectively) would have to be downrated, which would mean double punishment. Secondly, such an overlap appears inconsistent with the definition of PRMs and PAMs in ISO/IEC 15504-2 and ISO/IEC 33004, that two processes are to be two distinct lifecycle process concerns (see clause 3.1 for more explanation).

For the reasons above, in this HWE PRM/PAM there is no 'verification criteria' base practice on top of what

- HWE.1.BP1 already requires, which does include view 1

- BP1 in HWE.3 and HWE.4 already require, capturing view 2

### 3.3.3 Rationale 5 – No Usage of Terms Functional and Non-functional Requirement

There is no internationally agreed definition of the terms 'functional' and 'non-functional' (see various definitions and references below).

Assuming the definition in ISO IEC IEEE 29148 [25] and IREB CPRE [26], the terms 'functional' and 'non-functional' do not need to be used as a classification criterion, as this does not change anything in regards to e.g. subsequent requirements traceability, test case derivation etc.

However, there is a frequent need of having both functional and non-functional information in a

<sup>&</sup>lt;sup>1</sup> Also, the intacs<sup>™</sup> standardised course materials for Provisional Assessor qualification [29] explains why it is neither consistent with ISO/IEC 330xx or ISO/IEC 15504, nor good practice, to replace a BP rating by 'n.a.'. Also, rating this BP as Fully in absence of any such optional suggestions appears artificial in the light of base practices being defined as mandatory process performance indicators.

single requirement. This is what Note 1 and Note 8 in HWE.1 hint at.

Example:

■ #1 "The ECU shall be able to receive 100 to 110 bus messages per 1 [sec.]"

This requirement is complete, unambiguous, and verifable. Without the information of "100 to 110 bus messages per 1 [sec.]" the requirement would not be

- unambiguous because, from an architectural design perspective, it does matter how many messages must be able to be processed in a given timeframe,

- clearly verifiable because testing for the ability to receive a single message in a week's time or in 10 ms would both satisfy the functional content of the requirement.

Also, a situation that can be encountered is making two requirements out of it, such as

- #1a "The ECU shall be able to receive bus messages" (which can be viewed as "functional" acc.to ISO IEC IEEE 29148 [25])

- #1b "When receiving bus messages, the ECU shall be able to receive 100 to 110 per 1 [sec.]" (which can be viewed as "non-functional" acc.to ISO IEC IEEE 29148 [25] or "quality requirements acc.to IREB CPRE [26])

This would add requirements specification complexity without compelling additional value. Therefore, BP1 only refers to 'requirements' to cover the whole range of required information.

The following definitions can be found:

**ISO/IEC IEEE 29148** [25] defines in clause 5.2.8.3:

- 'Functional/Performance. ... describe the system or system element functions or tasks to be performed by the system. ...'

- Quality (Non-Functional) Requirements. Include a number of the 'ilities' in requirements to include, for example, transportability, survivability, flexibility, portability, reusability, reliability, maintainability and security.'

### The IREB CPRE [26] says that

- 'Non-functional *requirements*' is an umbrella term and, thus, represents 'quality requirements' or 'constraints'.

- Quality requirements are said to be e.g. performance, reliability, usability, portability.

In ISO/IEC IEEE 24765 [27] the following can be found:

- There are two definitions for 'functional requirement':

- 1. 'A statement that identifies what a product or process must accomplish to produce required behaviour and/or results'

- 2. 'A requirement that specifies a function that a system or system component must be able to perform'

- The definition of 'non-functional requirement' is

'A <software> requirement that describes not what the <software> will do but how the

<software> will do it.'

■ Non-functional requirements are further claimed to be synonymous to 'design constraints'.

### Automotive SPICE<sup>®</sup> [19]

- refers to the ISO IEC IEEE 24765 definition of 'functional'

- while not providing a definition of, or reference to another definition of, 'non-functional'

The **BGB** [20] says in clause 2.2.4.1 that

• ...non-functional requirements include for example quality requirements ... which are often used as criteria for acceptance tests.'

The systems engineering INCOSE Guide for Writing Requirements [28] informs:

'Types of requirement. Requirements that address capability and function may be expressed in a different manner to constraints and requirements specifying other system properties (often confusingly called 'non-functional' requirements – a term that will not be used again in this guide). The guide is intended to cover the whole range of requirement types.'

# 3.4 Rationales for HWE.2

# 3.4.1 Rationale 6 – One HW Design process (no separation between HW Architectural Design and HW Detailed Design)

In actual practice

- HW architectural design begins at the block diagram level, being the starting point for the detailed design. Detailed design is the level of information from which physical HW instances can be created, i.e. initial block diagrams do not reveal that level of detail.

- The entire HW designing process is performed iteratively. Technical details that originate from lower design levels such as schematics or layout (detailed design) might be added to block diagram models (architectural design) in order to provide further information for distinct verification and testing that are aimed to be done at the architectural level.

Further, note that the following assumptions would not serve as a motivation for separating HW architectural and detailed design at the level of a PRM:

- 1. "In their development processes companies may have extra activities for architectural and detailed design, mostly done iteratively with HW detailed design."

- A PRM/PAM does not represent a lifecycle model, see clause 3.1.

- A PRM/PAM is at the process-WHAT-level, while processes in companies are at the process-HOW-level. Therefore, it is the assessor's responsibility to map Assessment Indicators in a PAM need to the assessed context. See clause 3.1.

- 2. "Two processes would provide a better overview, i.e. a more orderly partitioning of topics"

- A PRM/PAM, by definition, does not represent a lifecycle model. Therefore, it is the assessor's responsibility to map Assessment Indicators in a PAM to information presented by projects and organisational units, see clause 3.1.

- HWE.2 has 10 BPs which is not extensive (some Automotive SPICE® v3.1 processes have 10 or more BPs, e.g. MAN.3, MAN.6, ACQ.11, ACQ.12, ACQ.13, SPL.2)

Also note that this HWE PRM/PAM does not represent an ECU level (see clauses 2 and 3.1).

For these reasons, at the level of a PRM, there is no necessity to separate HW Architectural Design and HW Detailed Design into two processes. The BPs needed to assess architectural and detailed design remain within HWE.2.

This is also consistent with the following models and standards:

- ISO 26262-5 [13]

- Swedish Standard SS 7740:2018<sup>2</sup>

- PISA<sup>3</sup>

- AIDA<sup>4</sup>

### 3.4.2 Rationale 7 – No System Hardware Process

In contrast to the Mechanical SPICE PAM [23], the HWE PRM/PAM does not consider a 'system hardware process' above HWE.2:

- See the reasons discussed above on 'Rationale 6 One HW Design process (no separation between HW Architectural Design and HW Detailed Design)'.

- See the explanations on the interpretation of the proper system level clause 3.7.

### 3.4.3 Rationale 8 – Mentioning of Special Characteristics

In this HWE PRM/PAM document, special characteristics are

■ directly represented by '11-HW02 Special characteristics'

<sup>&</sup>lt;sup>2</sup> The choice of the Swedish Standard SS 7740:2018 (being a PRM/PAM aiming for integrating elements from Automotive SPICE<sup>®</sup> PRM v 4.5 and PAM v2.5, and particular process-related clauses in ISO 26262:2011 1<sup>st</sup> Ed) was to also have a single hardware design process only (SE.ENG.5). This single process comprises BPs for both hardware architectural design and hardware detailed design.

<sup>&</sup>lt;sup>3</sup> In the PISA model (Process Improvement Scheme for Automotive, as proposed by the System & Software Evaluation Center, National Research Council of Italy), the "hardware segment" consists of four processes. Only one of them "...pertains to the definition of electronics design, including the preparation of the physical layout", namely HW1. There is no separation into HW architectural design and hardware detailed design at the process level; a distinction between HW architectural and detailed design is internal to HW.1.

<sup>&</sup>lt;sup>4</sup> Similarly to the Swedish standard SS7740, the Italian AIDA model explains itself both as a reference for reaching compliance with ISO 26262 and as a PAM for processes assessment. It defines a single PRM process "hardware design", i.e. no separation of a HW architectural and detailed design; the process "hardware architectural metrics" only covers the ISO 26262 clauses on HW architectural metrics and evaluation of safety goal violations due to random hardware failures.

required to be identified in HWE.2.BP6 "Evaluate the hardware architecture and the hardware detailed design"

In contrast to [23], in this HWE PRM/PAM document special characteristics do not receive their own dedicated BP. Reasons are that special characteristics are

- not the only concern that arises from hardware design evaluation

- very important, though not more significant than other aspects

### 3.4.4 Rationale 9 – Evaluate Instead of Verify

In [23] for the architecture and design-oriented processes a BP was introduced about 'Verify ... design', the purpose of which is to ensure that the mechanical architectural design and mechanical component design, respectively, meet the 'upper-level requirements'.

In this HWE PRM/PAM such a base practice is not introduced in favour of an 'evaluate design' BP. The reasons are that verifying whether a design meets the requirements

- is already represented by the BPs on 'consistency', 'allocate', and 'traceability' together with the directives in the BGB [20] clause 2.1.1

- as such does not address the necessity of evaluating a design in terms of unearthing further issues or critical findings during design creation (e.g. a FMEA can identify risks that give rise to new requirements not coming from the system level, design changes, and additional test cases etc.)

### 3.4.5 Rationale 10 – No BP on Evaluating Alternative Architectures

For HWE.2 a base practice 'Evaluate alternative architectures' has not been introduced for the following reason:

■ HWE.2.BP1 requires to describe the rationale for the decided hardware architecture. It is considered of higher practical value to give arguments why a given design was chosen rather than particularly explaining which other approaches were not chosen. Further, it can be considered that the former implies the latter.

# 3.5 Rationales for HWE.3 and HWE.4

# 3.5.1 Rationale 11 – ISO 26262 Evaluation of HW Elements is not an alternative for HWE.3 and HWE.4

The processes in this PAM

- do not take a single HW element perspective. This is because 'hardware element' in this PAM can denote a HW part, a HW component, or the complete hardware (see Section 1.8).

- are not restricted to safety-related products or contexts, so for hardware development this HWE PRM/PAM, respectively, represents what ISO 26262 calls 'evidence of compliance with standards that support quality management' [ISO 26262-8:2018 clause 5.3.2 example 2].

Clause 13 in ISO 26262-8:2018 addresses how to proceed with a procured individual HW element that is supposed to be used in a safety-related product. Therefore, hardware part evaluation according to ISO 26262-8:2018 clause 13 is complementary to this HWE PRM/PAM and does not contradict it.

### 3.5.2 Rationale 12 – HW Integration

Integration in terms of software or mechanical lifecycle processes is understood as a stepwise assembly of a product, and performing tests along, or in between, the assembly steps. This notion is not always applicable per se to hardware development. Rather, a HW often is fully assembled first, and then HW testing is performed on the fully assembled hardware by e.g. using measuring points inside the HW to test the inputs and outputs with variations.

Further, testing of a single HW element always includes the testing of the interfaces as such tests need electrical input signals and output load. This means, there is no conceptual distinction between 'testing a single HW element in isolation' and 'testing interfaces between HW elements.

Thus, in order to avoid confusion and speculation we do not use the term 'integration' in the context of HWE.3.

The processes HWE.3 and HWE.4 can be mapped to ISO 26262-5 [13] clause 10.

See also Rationale 6 – One HW Design process (no separation between HW Architectural Design and HW Detailed Design).

# 3.5.3 Rationale 13 – Choice of the term 'Verification' for right-hand side HWE Processes

During the development of Automotive SPICE®, the VDA Working Group 13 suggested that SYS.4 "System Integration Testing" and SYS.5 "System Qualification Testing" should remain testing processes, and that any other verification approach (that can also be considered applicable at the system level such as measurements, simulations etc.) should be dealt with in the context of SUP.2 "Verification". Reasons were e.g. downward compatibility to Automotive SPICE® 2.5.

However, in this document the right-hand side HWE processes cover testing as well as measurements, calculations, simulations, reviews, and analyses and therefore are called 'verification'.

The reasons are:

- The intacs<sup>™</sup> HWE PRM/PAM working group has no means to change Automotive SPICE<sup>®</sup>, and for copyright reasons does not intend to copy entire process definitions from Automotive SPICE<sup>®</sup> (such as SUP.2) to be enhanced. Therefore, there would have been no intuitive way in this document to convey to the assessor how a ready-to-use adaptation of SUP.2 would be formulated.

- 2. In HW development, testing is neither the only nor the main verification approach. Therefore, separating testing from other verification measures would

- not intuitively reflect the current state-of-the-art HW development;

- increase reading complexity and reduce assessment efficiency as, during an assessment, indicators in two different processes would have to be looked at consistently.

- 3. Automotive SPICE® allows for an exception for the software sub-domain: in SWE.4 'Unit Verification' a SW unit can be verified coherently by means of a combination of static verification, testing, or code reviews (a view that is also reflected in ISO 26262-6 [14] clause

9)<sup>5</sup>. The HWE PRM/PAM, also being a sub-domain, correspondingly adopts this view (see 2. above).

4. The concept of separating SYS.4 'System Integration Testing' and SYS.5 'System Qualification Testing' from other verification aspects at the system level, as well as in the PAM for mechanical engineering [6], can still be maintained. Allowing an integrated and coherent verification approach for processes in the software and hardware sub-domains technically does not interfere with that.

### 3.5.4 Rationale 14 – ISO 26262-8 Verification Planning vs. HWE PRM Outcome 'Strategy'

The aspects listed in BP1 'strategy' of both HWE.3 and HWE.4 are mapped to ISO 26262-8 clause 9.4.1.1 'Verification Planning'. This could delude the reader into thinking that this PAM would erroneously reference PA 2.1 aspects at CL2. However, this is only a matter of naming. Conceptually, ISO 26262-8 clause 9.4.1.1 does relate to what a SPICE PRM/PAM call 'strategy'.

# 3.6 Addressing the Mixture of Requirements and Design

A requirement denotes a feature of an element from an external black-box perspective, at a given level of abstraction. In contrast, design denotes the technical solution in the white-box for the same element at the same level of abstraction. Requirement thus describe the 'What' while design describes the 'How' for a given element at the same level of abstraction (see 3.1).

What can be encountered in the automotive industry is that a document titled 'requirements', e.g. from a customer,

- mixes different levels of abstractions

- contains white-box (i.e. design-restricting) statements

- contains statements that are not in the delivery scope of the supplier

Therefore, it is recommended to put great emphasis on Automotive SPICE® SYS.1, especially BP2 and BP3:

- BP2 "Understand stakeholder expectations. Ensure that both supplier and customer understand each requirement in the same way"

- BP3 "Agree on requirements. Obtain an explicit agreement from all relevant parties to work on these requirements"

Thus, it is suggested that the stakeholder input (e.g. a customer specification) should be sorted in such a way that the conceptual difference of requirements and design is preserved, and the information is allocated to appropriate work products at the proper level of abstraction (see Figure 6).

<sup>&</sup>lt;sup>5</sup> ISO 26262-5:2018 presents a 'hybrid view' here: on the one hand, the title of ISO 26262-5 clause 10 being 'HW integration and verification' instead of 'testing' was deliberately chosen. On the other hand, the method tables in clause 10 are related to 'testing'. Then again, however, clause 10.4.1 clearly says that any hardware verification activity shall be performed in accordance with ISO 26262-8:2018, clause 9 which is about verification in general terms. ISO 26262-8:2018 clause 9 'Verification' is clear on that it addresses both the left and right branches of the V model, thereby representing an umbrella term comprising testing, verification reviews (an ISO 26262 term associated with quality assurance of work products) etc.

Figure 6 – Reallocation of stakeholder requirements

# 3.7 Notion of 'System' above HWE Processes

The Scope of this HWE PRM/PAM (see clause 2) was designed to be able to serve as a candidate for a hardware plug-in solution proposal for Automotive SPICE<sup>®</sup> (see clause 2). In turn, Automotive SPICE<sup>®</sup> provides system level processes (SYS.x) which are generic, i.e. are not bound to a particular system boundary (see also clause 3.1).

Therefore, the system boundary for

- 1. A **semiconductor supplier** would be e.g. a microcontroller or a system-on-chip. This system boundary should be reflected in the Automotive SPICE® SYS processes because besides hardware it typically comprises a mechanical housing, firmware etc. The HWE PRM/PAM should then be used to reflect the hardware-related interior of this system. In this context, the definition of 'hardware part' and 'hardware component' can represent ISO 26262's notions of 'hardware subpart' and 'hardware elementary subpart'.

- 2. A **control device supplier** would be the ECU. This system boundary should also be reflected by the Automotive SPICE® SYS processes because it typically comprises hardware, software, housing, connectors etc. In consistency with the scope of this document, the HWE PRM/PAM should then be used to reflect development of the fully assembled PCB. In this respect, the definitions of 'hardware part' and 'hardware component' in this document apply.

- 3. A **mechatronic system supplier** would be the mechatronic product. Both the mechatronic system boundary and the ECU system boundary would be reflected by separate process instances of the Automotive SPICE® SYS processes in a decomposed manner. To the ECU system boundary within the mechatronic system the considerations in 2. above apply.

# 3.8 Agile Approaches

This HWE PRM/PAM is not in contradiction with any agile principles, approaches, or practices. See [20] clause 2.2.2 'Agile Environments' and [30] for the detailed explanations and arguments.

# 3.9 ISO 26262 Mapping

### 3.9.1 References

References are made to ISO 26262 Parts 5, 8, 9, and 11 [13], [15], [16], [17]. Note that only references can be made to ISO 26262 clauses that have, or contain, a process-related content<sup>6</sup> or define ISO 26262 terminology; the reason is that a PRM/PAM generally define process principles but not technical or method requirements (see ISO/IEC 33004 [4], and the differentiation between the WHAT and the HOW levels in [19]). This should facilitate the mutual consideration, or even mutual reuse, of SPICE assessment and safety audit results for the purpose of making such (e.g. combined) process assessments and safety audits more efficient while reducing interview effort. See also ISO 26262-2 [11], clause 6.4.11.4, f), Notes 3 and 4 here. These references are meant neither to represent nor to trigger a model fusion, nor to suggest additional assessment indicators for this PAM. In this respect, the given references are not meant to be exhaustive.

### 3.9.2 ASIL Method Tables

This document does not repeat, or refer to, any table in ISO 26262 part with methods classified by ASILs. Reasons:

- Repeating of method tables in ISO 26262 or any other standard

- would introduce redundancy

- might entail a copyright issue

- ISO 26262:2018 clause 4.3 makes it clear that the methods listed in the method tables are only recommendations. This means that any method can be chosen (i.e. not necessarily those recommended or highly recommended in ISO 26262) as long as an argument can be presented that the used methods fulfil the requirements listed in the corresponding ISO 26262 clause above a method table. If such a rationale can be given, a further rationale for omitted methods is not necessary (see clause 4.3 "Interpretation of Tables" in all Parts of ISO 26262:2018from Part 2 to Part 9).

### 3.9.3 ISO 26262 Semiconductor Perspective

This document does not use the terms

- hardware subpart

- hardware elementary subpart

Further, this document does not follow the ISO 26262-1 definitions as is of

<sup>&</sup>lt;sup>6</sup> The German VDA/DIN NA 052-00-32-08 subgroup represents the German national standardization body on Functional Safety according to ISO 26262. This subgroup has classified the ISO 26262 clauses according to a categorisation schema of "process", "technical", "both", "reference". The purpose was to facilitate use cases of combined Automotive SPICE<sup>®</sup> process assessments and safety audits, and mutual consideration of SPICE assessment and safety audit results for the purpose of making such process assessments and safety audits more efficient while reducing interview effort in practice.

- hardware part

- component

#### Reasons:

The ISO 26262:2018 terms 'hardware subpart' and 'elementary subpart' were introduced in Part 1 order to support ISO 26262-11:2018 and align it with ISO 26262-5:2018. Correspondingly, the ISO 26262 term 'hardware part' is explained as a '*portion of a hardware component at the first level of hierarchical decomposition*' above 'hardware subpart' and 'elementary subpart'<sup>7</sup>. Hierarchical decomposition of elements is a concept also supported in this document (note: 'hierarchical decomposition' does not relate to ASIL decomposition in ISO 26262:2018).

Perspectives on how to understand a system level above the HWE processes, see clause 3.7.

### 3.9.4 ISO 26262-1 term 'Item'

The term 'item' is defined fundamentally differently in ISO 262626 and Automotive SPICE®. In this document, we follow the Automotive SPICE® definition for the following reasons:

- a) This document is an ISO/IEC 33004 [4] compliant PRM/PAM (see section Annex B), just as Automotive SPICE®, while ISO 26262 is not. Further, this HWE PRM/PAM document can be used as a plug-in proposal for the Automotive SPICE® plug-in concept. It is thus meaningful to be primarily consistent with the Automotive SPICE® terminology.

- b) This document includes a PRM/PAM for electrical and electronic elements (see clause 2 and a) above). The term 'item' in ISO 26262 rather relates to the system or product level.

# 3.10 Automotive SPICE<sup>®</sup> PAM

### 3.10.1 Traceability and Consistency

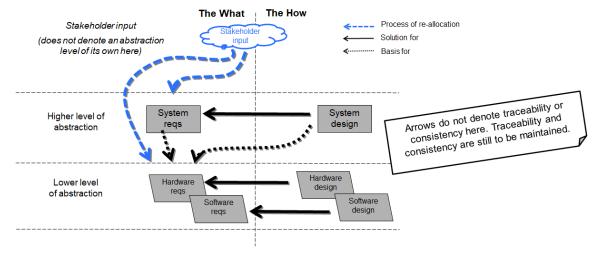

The traceability and consistency within the HWE PRM/PAM, and in connection with Automotive SPICE® processes, is as depicted below.

<sup>&</sup>lt;sup>7</sup> In [19] neither the definition of 'component' nor 'software component' mentions the possibility of hierarchical decomposition.

Figure 7 – Traceability and consistency in the HWE PRM/PAM in relation to Automotive SPICE®

### 3.10.2'Agree' and 'Summarise and Communicate'

Automotive SPICE<sup>®</sup> [19] Annex D.5 applies correspondingly.

### 3.10.3 'Evaluate', 'Verification Criteria', and 'Ensuring compliance'

Automotive SPICE<sup>®</sup> [19] Annex D.6 applies correspondingly for HWE processes in this document. However, note the 'Rationale 3 – Requirements Characteristics at CL1'.

### 3.10.4 The relation between 'Strategy' and 'Plan'

Automotive SPICE<sup>®</sup> [19] Annex D.7 applies correspondingly.

# 3.11 VDA BlueGoldBook 'Automotive SPICE® Guidelines' [20]

### 3.11.1 Assessment Scoping

Sections 1.1 and 1.2 [20] apply to this document as is.

### 3.11.2 Rating Practice

Section 1.3 in [20] apply to this document as is.

### 3.11.3 Rating Text Patterns

Section 1.4 in [20] also applies.

### 3.11.4 Rating Rules and Recommendations

The rules (RLs and RCs) in the following clauses in the BGB [20] apply correspondingly to the HWE PRM/PAM:

- 2.1.1

- 2.1.2

- 2.1.4

# 4 Process Reference Model, Performance Indicators (CL1), Rating Rules, Rating Recommendations

See 'Rationale 1 – No Production Process'.

See 'Rationale 2 – No Procurement Process'.

### Editorial guidance

The processes in the process dimension can be drawn from the PRM, which is incorporated in the tables below indicated by a red bar at the left side.

Analogously to Automotive SPICE<sup>®</sup>, each table related to one process in the process dimension contains the PRM (indicated by a red bar at the left side) and the process performance indicators necessary to define the PAM. The process performance indicators consist of BPs (indicated by a green bar) and output work products (indicated by a blue bar). Note that if an output work product indicator given here does not appear in Annex A then it represents the corresponding work product indicator in Automotive SPICE<sup>®</sup> [19].

Rating rules and recommendations are presented separately as they are not an element of a PRM or PAM [4].

# 4.1 HWE.1 – Hardware Requirements Analysis

Refer to rationales in clause 3.3 and to clause 3.6.

| Process ID          | HWE.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Process name        | Hardware Requirements Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |